이번 포스팅에서는 반도체 칩을 만들기 위한 설계 과정에 대해 알아보자.

회로설계 엔지니어라면 전반적인 flow를 파악하고 있어야 하지만,

실무를 하다 보면 "내가 하는 일"만 생각하게 된다..

앞으로 알아볼 전반적인 flow에 대해 알고 있으면 보다

넓은 안목으로 후에 발생할 문제들에 대해 대비한 robust 한 회로를 설계할 수 있다.

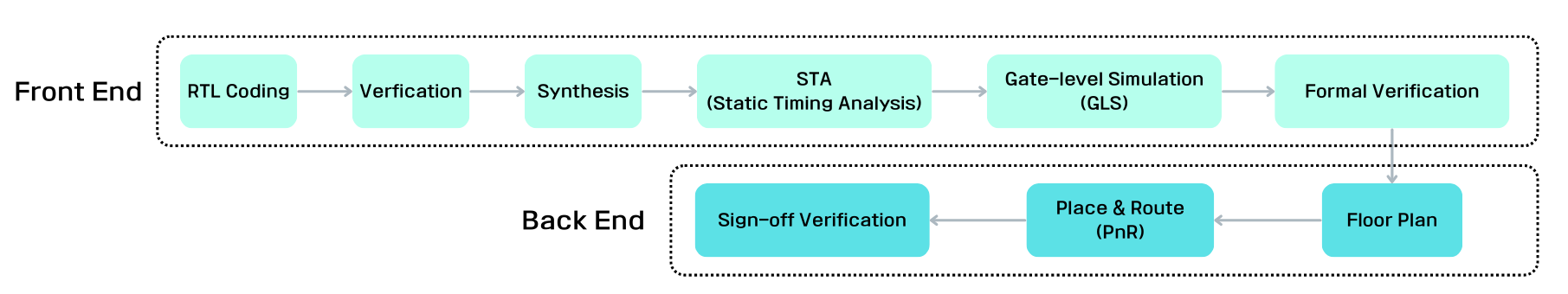

반도체 칩 설계 Flow

반도체 칩은 크게 위와 같은 flow에 따라 설계된다. RTL Coding > Verification > Synthetis > STA > Gate-level Simulation > Formal Verification 까지가 front-end 단계이고, 이후 Floor Plan > P&R > Sign-off Verification이 back-end 단계이다.

각 단계에 대해 더 자세히 알아보자.

1. RTL Coding

반도체 칩은 하드웨어 프로그래밍 언어 (Hardware Description Language, HDL)를 이용하여 작성된다. 대표적인 HDL 언어로는 VHDL과 Verilog가 있다. 보통의 경우 Verilog를 더 많이 사용하는 것 같다.

# HDL 이란?

HDL (Hardware Description Language)은 하드웨어를 설계하고 동작을 기술하기 위해 사용되는 프로그래밍 언어이다. 주로 디지털 회로를 설계하는 데에 사용되며, 하드웨어의 구조, 동작, 타이밍 등을 기술하는데에 적합하다. HDL은 보통의 소프트웨어 프로그래밍 언어와 다르게 병렬 처리가 가능하다는 특징이 있다.

2. Verification

HDL로 하드웨어를 제대로 설계했는지 확인하기 위해 검증의 단계를 거친다. 각 모듈의 논리적 동작을 확인하게 되고 testbench와 DUT를 통해 시뮬레이션 waveform을 확인하게 된다. RTL simulation을 위해 사용되는 툴은 Siemems사의 Modelsim, Cadence사의 Xcelium, Synopsys사의 VCS(Verilog Compiler Simulator) 등이 있다. 학부 수준에서는 무료로 사용 가능한 Modelsim을 주로 사용한다. 보통 컴파일 단계를 통해 문법적 오류가 없는지 확인하게 되고, waveform을 통해 의도한 대로 동작하는지 확인한다.

3. Synthesis

Synthesis는 합성 단계이다. 합성은 RTL을 AND/OR/NOT/NAND/NOR 등의 gate-level netlist로 변환하는 과정이다. 이는 프로그래밍 언어로 작성된 모델을 실제 하드웨어 칩으로 만들기 위한 과정이다. 이 때, clock, power나 timing constraint을 고려하여 변환된다. RTL 합성을 위해 사용되는 툴은 Synopsys사의 Design Compiler, Xilinx사의 Vivado 등이 있다. 합성을 진행하게 되면 결과적으로 하나의 netlist 파일과 slack, area 등의 정보가 있는 report들이 추출된다. 이를 통해 gate count 등을 계산할 수 있다.

4. STA (Static Timing Analysis)

STA는 Static Timing Analysis의 약자로 말 그대로 timing을 분석하는 과정이다. 하드웨어 칩에서는 실제로 clock을 포함한 signal들이 달려가는 데에 소요되는 physical 한 시간이 존재한다. 또한, 다양한 on/off chip skew, noise 등등 ideal 한 RTL simulation 환경과는 다른 변수들이 있기 때문에 이를 고려하여 timing 분석을 진행해야 한다. "Static" timing 분석이기 때문에 실제로 다양한 패턴에 따라 toggle 하는 data를 사용하지 않고 회로의 timing path만을 계산하여 분석하는 과정이다. 대표적으로 setup/hold timing을 보게 된다. 이와 관련하여서는 다음에 더 자세히 다뤄보도록 하겠다. STA는 Synopsys사의 PrimeTime이라는 툴을 가장 많이 사용한다.

5. Gate-level Simulation (GLS)

합성 및 STA까지 진행한 후에 다시 시뮬레이션을 진행하게 된다. 이 단계를 gate-level simulation, 즉 GLS라고 한다. RTL 시뮬레이션에서는 실제 cell delay나 propagation delay 등을 고려하지 않고 ideal 하게 진행된다. GLS에서는 Standard Delay Format (SDF)라는 파일에 타이밍 정보를 포함하여 gate-level로 시뮬레이션을 진행하기 때문에 보다 정밀한 타이밍 및 동작 검증이 가능하다. 하지만 그만큼 시뮬레이션에도 오랜 시간이 소요되고 디버깅하는 것도 RTL 시뮬레이션 대비 어려움이 있다.

6. Formal Verifiaction

이제 gate-level netlist까지 나왔으니 합성이 잘 되었는지 확인해보고 싶지 않은가? 이때, 합성 전후의 결과가 동일한지 확인하기 위한 검증단계를 거친다. Synopsys사의 Formality라는 툴을 이용해서 RTL과 netlist의 동등성을 확인할 수 있다.

7. Floor Plan

이제부터는 physical design을 하는 back-end 설계 단계이다. FloorPlan은 실제 칩 레이아웃에 배치하는 초기 단계이다. 각 모듈의 위치나 형태 등을 결정하고, 컴포넌트 간 연결 방법을 정의한다. PPA를 개선하기 위해 FloorPlan 단계에서 효율적으로 배치하는 것이 중요하다.

8. Place & Route (PnR)

P&R(Place and Routing) 단계에서는 셀을 배치(Placement)하고 배선(Routing) 작업을 진행한다. 이 과정에서 timing 성능과 전력 소비 등을 고려하여 최적화해야 한다. 또한, 칩의 면적은 곧 가격과 직결되기 때문에 비용을 절감하는 동시에 성능을 유지하기 위해 노력해야 한다.

Placement 단계에서는 standard ccell들을 물리적 영영에 배치하게 된다. 이때, timing 경로, 전력 분배, 배선 복잡성 등을 고려하여 배치하게 된다. Timing critcal path에서 timing 문제가 발견되면 셀의 위치를 조절하거나 timing을 최적화하게 된다.

Routing 단계에서는 배치가 완료된 후에 셀 사이를 물리적으로 연결하게 된다. Clock과 전원(VDD/VSS)이 안정적으로 cell에 공급될 수 있도록 배치한다. 이 때, CTS(Clock Tree Synthesis)가 아주 중요한 작업인데 이는 clock buffer 등을 통해 clock 신호가 모든 flip flop에 동시에 도달할 수 있도록 보장하는 것이다. CTS를 통해 clock 간 skew를 최소화하는 것이 중요하다. 배선 작업이 완료되면 DRC(Design Rule Check) 과정을 통해 설계 규칙을 검토하게 된다. 설계 규칙이라 함은 예시로 배선간에 요구되는 최소한의 간격이다.

9. Sign-off Verification

마지막으로 Sign-off Verification 단계는 최종적으로 제조를 시작하기 전에 설계가 제대로 진행되었는지 확인하는 매우 중요한 단계이다. 요구되는 스펙(specification)을 충족하는지, 실제로 제조가 가능한 상태인지 확인하는 최종 점검 단계이다. 이 단계에서는 아래와 같은 내용들을 검증한다.

- Timing Analysis

- Power Analysis

- Signal Integrity Analysis

- IR Drop

- Physical Verification

- Thermal Analysis

'공부 기록 > 회로설계' 카테고리의 다른 글

| [Verilog] 베릴로그 function vs task (0) | 2024.08.05 |

|---|---|

| 반도체 회로설계 헷갈리지만 중요한 개념, jitter, skew, slack, slew 란? (0) | 2024.07.31 |

| Verilog에서 C code 사용이 가능한 Direct Programming Interface (DPI) 개념 및 사용법 (1) | 2023.06.01 |

| 하드웨어 검증 언어, System Verilog 란? - Testbench, DUT (0) | 2022.12.16 |

| [Verilog] reg vs wire - reg와 wire의 차이점 (0) | 2022.05.05 |