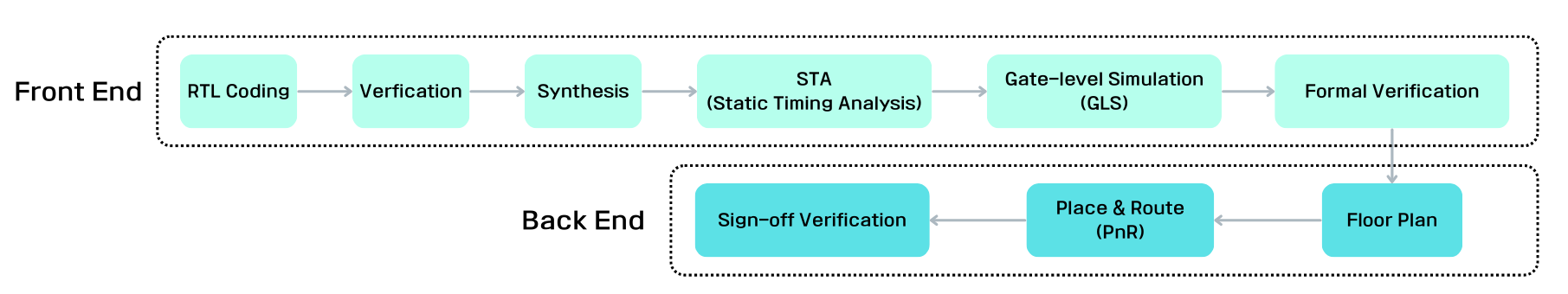

이번 포스팅에서는 반도체 칩을 만들기 위한 설계 과정에 대해 알아보자.회로설계 엔지니어라면 전반적인 flow를 파악하고 있어야 하지만,실무를 하다 보면 "내가 하는 일"만 생각하게 된다.. 앞으로 알아볼 전반적인 flow에 대해 알고 있으면 보다넓은 안목으로 후에 발생할 문제들에 대해 대비한 robust 한 회로를 설계할 수 있다. 반도체 칩 설계 Flow 반도체 칩은 크게 위와 같은 flow에 따라 설계된다. RTL Coding > Verification > Synthetis > STA > Gate-level Simulation > Formal Verification 까지가 front-end 단계이고, 이후 Floor Plan > P&R > Sign-off Verification이 back-end 단계..