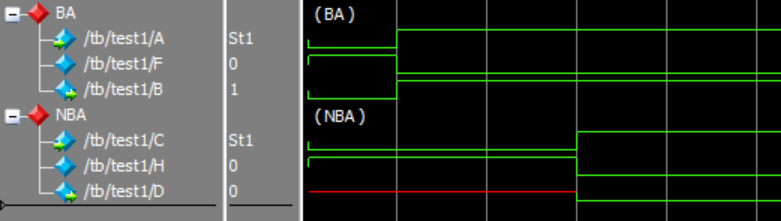

Procedural assignment의 종류에는 blocking assignment와 non-blocking assignment가 있다. 각 할당문과 그 차이에 대해 알아보자. 1. Blocking Assignment " 기술된 순서대로 동작하는 할당문 " Blocking assignment는 그 이름에서도 알 수 있듯, 현재 statement가 수행되는 동안 block 처리가 되어 다음 statement가 수행되지 않는다. 따라서, 다음 statement에서는 업데이트된 값을 사용하며, 기본적으로 zero-delay를 갖는다. 할당 연산자 = 을 사용한다. 2. Non-Blocking Assignment " 기술 순서와 무관하게 동시에 수행되는 할당문 " Non-Blocking assignment는 ..