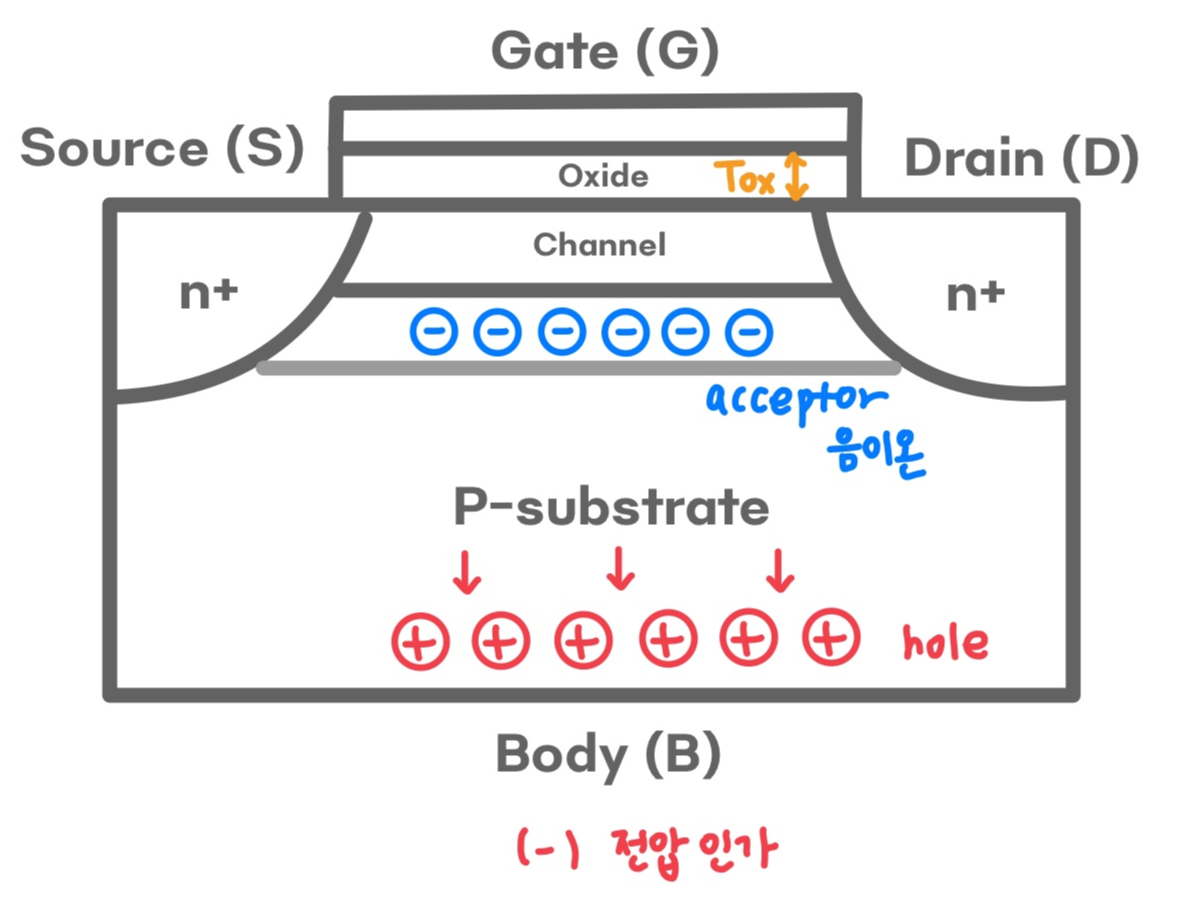

최근 공정이 미세화되어 누설 전류가 생기는 현상이 발생한다. 누설전류가 발생하면 동작 속도가 느려지고 소자의 성능이 저하된다. 이러한 현상을 short channel effect라고 한다. 본 포스팅에서는 SCE의 대표적인 4가지인 DIBL, GIDL, Velocity Saturtion (속도포화), Hot Carrier Injection 효과에 대해 알아보자. 0. Short Channel Effect (단채널효과) 반도체 소자가 작아질수록 같은 웨이퍼 면적에 더 많은 칩을 생산할 수 있어 원가절감이 되고, 소자가 미세화 됨에 따라 속도 증가 및 전력 소모가 감소하여 성능이 개선된다. 하지만 MOSFET에서 채널 길이가 너무 짧아져서 전기장과 공핍층의 중첩이 발생하여 누설 전류가 생기는 현상이 발생하는..